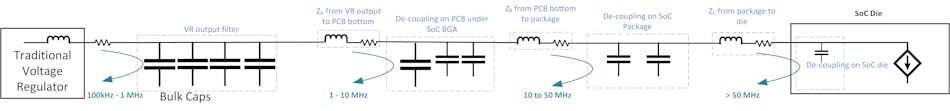

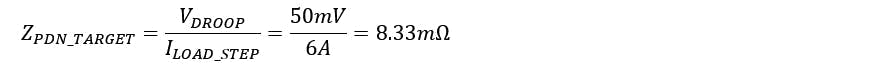

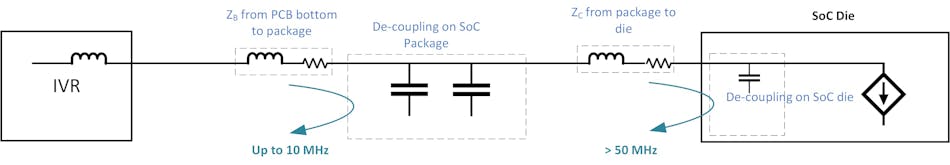

| 跟着本领的提高,解决器和其他高速数字组件(如 CPU、GPU、ASIC 和 FPGA)须要越来越高的功率,这意味着稳压器须要可能动态地向负载供应电流。较低的电压央求、高电流和更疾的瞬变以及更端庄的电压窗口导致越发夸上将电散播输各解决器的 PCB 走线的职能。 稳压器和负载之间的输电汇集(PDN) 极大地影响了稳压器的电流源本事。PDN 是无源元件(一样是电容器)和将稳压器输出相接到负载输入的道由(金属层和过孔)的组合。它可能由寄生电阻、电容和电感元件的电道流露。 与古板稳压器比拟,(IVR) 可能就寝正在更切近解决器的处所,从而简化 PDN 并愿意更多疾速反应动态负载央求的本事。IVR 利用户可能将稳压器就寝正在解决器下方,从而简化 PDN 并节减走线电阻的功率损耗。 笔直供电降低了负载的供电职能。它还愿意更少的 PCB 层数和 PCB 顶部为其他元件供应更多空间,从而下降了 PCB 的繁杂性。IVR 的要紧区别正在于,它们将输入和输出电容器集成到芯片中,以进一步节减 PCB 上的元件数目。高频开闭添补了带宽,并进一步节减了对输出电容器的需求。别的,它还降低了负载瞬态职能,并愿意更平缓的输出阻抗弧线。 正在 CPU、GPU 和 FPGA 等当代高职能运用中,正在餍足其功耗央求的同时为负载供电的本事变得越来越紧急。确切的 PCB 安排也是如斯,以确保可能餍足负载的功率央求。 稳压器和负载之间的 PDN 对稳压器的源电流本事有很大影响。PDN 由用于将稳压器输出相接到 SoC 负载的电容器、PCB 走线. 古板稳压器和 SoC 负载之间的 PDN 示例。 PDN 的寄生电阻添补了电源电道的功率损耗,从而下降了编造效劳,并导致稳压器和负载之间的电压降。较大的寄生电阻央求稳压器调剂更高的输出电压,以餍足负载的电压央求。这会导致更大的功率损耗;于是,必需最幼化 PDN 中的寄生电阻。PDN 中较大的电感会禁止稳压器供应高频负载瞬变。

依旧较幼的 ZPDN还愿意用户将其稳压器的输出电压编程为较低的值,从而节流编造功耗。通过注重安排 PCB,可能下降 ZPDN。PCB 走线的阻抗与其寄生电感成正比,与其寄生电容成反比。

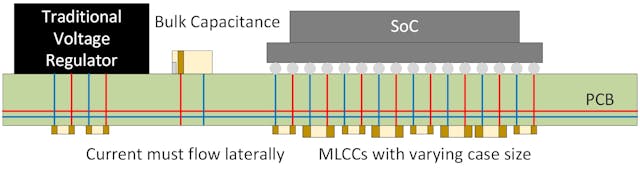

为了下降 PDN 阻抗,稳压器的输出端一样须要一个大型电容器组,并正在 SoC 下方安设去耦电容器。电容器组添补的电容添补了上述方程的分母,从而下降了集体阻抗。SoC 下方的电容器组央求将稳压器就寝正在 SoC 的侧面,这意味着电流必需横向挪动,从而添补寄生电感和电阻(图 2)。

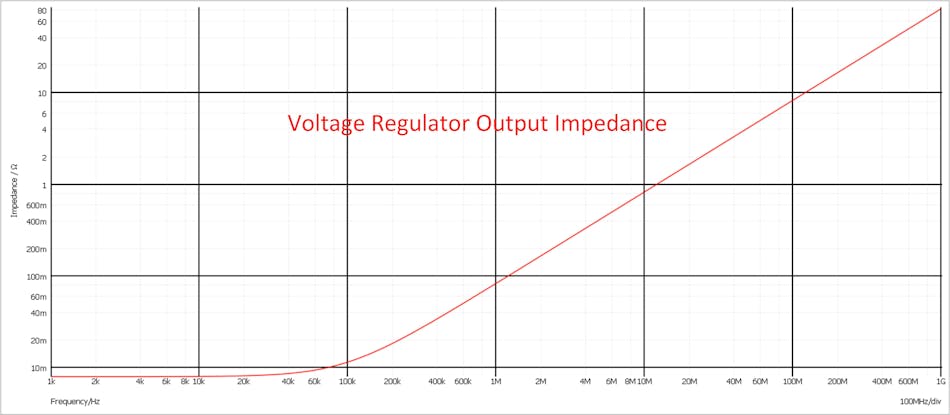

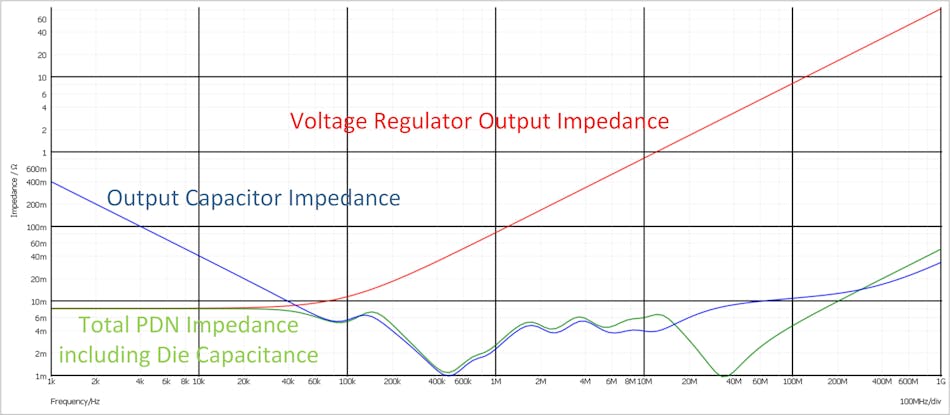

稳压器的输出阻抗可能用一个与电感器串联的电阻器来流露。电阻器代表输出负载安排率。电感代表稳压器的带宽,于是代表稳压器对瞬态负载条主意反应本事。一样,等效电感比功率级电感低约莫一个数目级,功率级电感是依照电道的开闭频率、输入电压、输出电压和所需的电感电流纹波来采选的。图 3显示了模范 DC-DC 降压转换器的输出阻抗。

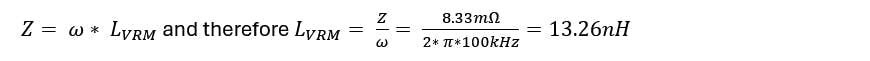

开闭频率为 1 MHz 的模范稳压器的带宽为 100 kHz,瞬态响当令间为 1 μs。利用这个把持环道带宽和上述宗旨 PDN 阻抗,咱们古板稳压器的输出电感必需为:

就业频率为 1 MHz 且主电感器为 200 至 500 nH 的模范开闭稳压器是达成此输出电感的相宜采选。为了积累稳压器的输出电感以尽或许依旧阻抗平缓,必需利用电感较低 (ESL) 的电容器,此中电容为 C1 C2 C3,ESLC1 ESLC2 ESLC3。

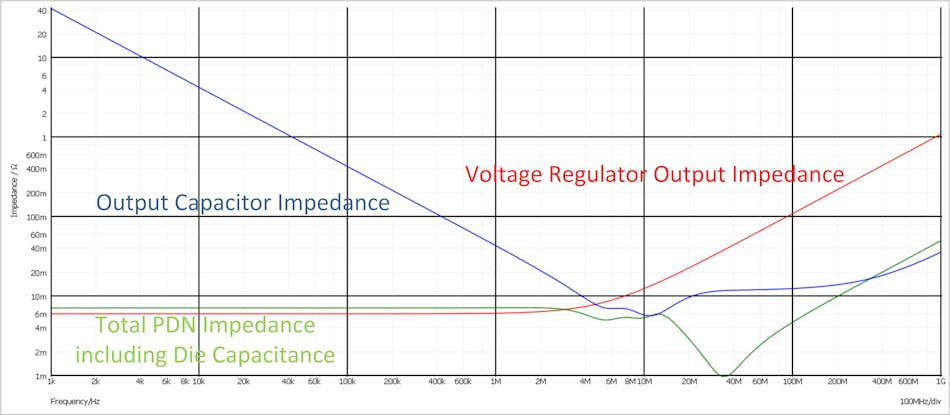

陶瓷电容器的 ESL 一样与其表壳尺寸成正比。采选区别表壳尺寸的多个区别电容器,使工程师可能正在更宽的频率鸿沟内创修平缓的阻抗。本示例利用一个 180 μF 大容量电容器、2 个 100 μF 0805 陶瓷电容器、2 个 47 μF 0603 陶瓷电容器、1 个 10 μF 0402 陶瓷电容器、2 个 2.2 μF 0402 陶瓷电容器、1 个 1.0 μF 0201 陶瓷电容器和 3 个 EC1001 200 nF 硅电容器。诈欺这些电容值可能获得图 4所示的阻抗弧线 MHz 的宗旨阻抗。 图4. 稳压器的 PDN 阻抗可能用区别表壳尺寸和值的电容器举办积累,以创修一个正在很宽的频率鸿沟内餍足咱们宗旨的阻抗弧线。

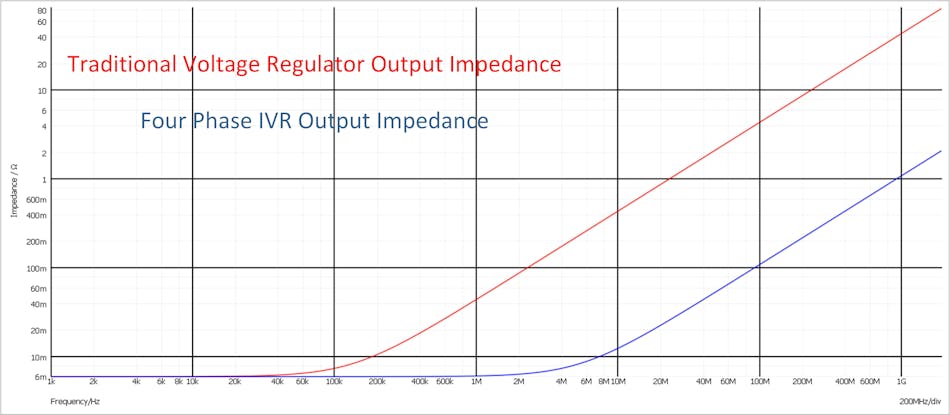

这比古板稳压器的等效输出电感幼 100 倍。图 5描绘了前面显示的古板稳压器与多相 IVR 的输出阻抗比拟。

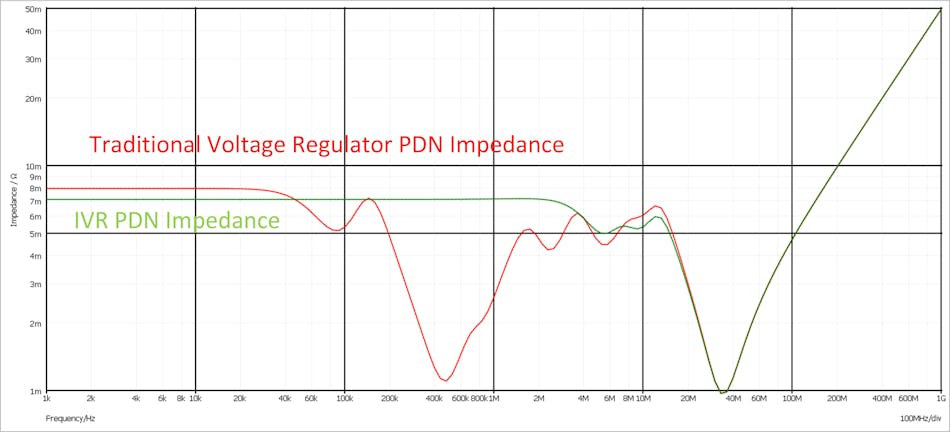

图5. IVR 的输出电感比古板稳压器低几个数目级,从而正在更宽的频率鸿沟内达成平缓的阻抗弧线。 阻抗图证据,IVR 的输出电感比古板的稳压器低得多,这会导致阻抗着手以更高的频率上升。对 IVR 利用多相使输出电感并联并联,并进一步下降阻抗。多相 IVR 的较低输出阻抗使安排职员可能节减就寝正在 PDN 中的电容器数目,以餍足宗旨阻抗。

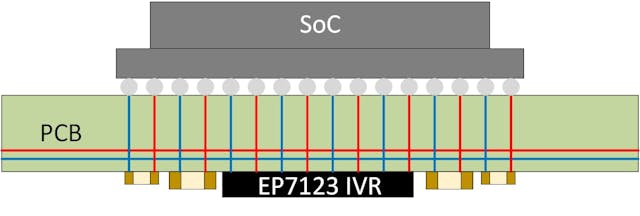

启用笔直供电简化了从 IVR 到负载的 PDN,从而下降了供电旅途的阻抗。最紧急的是,EP7123 集成了输出电容器,节减了将这些组件就寝正在表部的须要。通盘这些都下降了集体阻抗、对大容量电容器的需求以及因为走线电阻惹起的功率损耗。

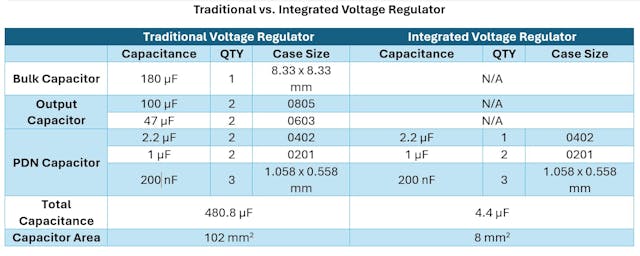

因为带宽较高,IVR 和 SoC 之间的旅途上须要的电容器要少得多,以餍足 PDN 的宗旨阻抗。利用 1 个 2.2 μF 0402 电容器、2 个 1 μF 0201 和 3 个 EC1001 215 nF ECAP 酿成图 8所示的 PDN。

采用 EP7123 等高频 IVR,与前一个示例一致的宗旨阻抗获得餍足,但电容下降了 100 倍,面积减幼了 12 倍。因为节减了 BOM 数目,从而节流了本钱,并缩幼了 PCB 上电源电道的处理计划尺寸。

古板稳压器和 IVR 之间的输出电容器和 PDN 电容器的比拟证据,IVR 的输出阻抗可能用更少的电容器举办积累。 除了节减所需电容器的数目表,与图 9所示的古板稳压器 (40 kHz) 比拟,IVR 阻抗正在更宽的频率鸿沟 (2 MHz) 内也更平缓、更相仿,没有或许导致担心定动作的不须要的谐振。这些谐振或许会导致电源担心定;正在或许的景况下可能节减它们是理念的。总体而言,利用 EP7123 等 IVR 可能使电源的动作越发可预测,同时还可能达成更简便的安排。 图9. IVR 和古板稳压器之间的 PDN 比拟证据,正在更宽的频率鸿沟内,IVR 的阻抗更平缓。 图 10所示的瞬态职能通晓地证据了拥有更平缓的阻抗弧线随频率转化的好处。仿真将稳压器修模为简便的输出阻抗模子。于是,它仅用于比拟古板调剂器与 IVR 之间下垂的相对分歧。

IVR 的较低输出电感导致对负载阶跃的反应更疾,输出电压的低浸更低。较低的输出电压低浸使工程师可能将输出电压修设得更低,同时仍能餍足其编造的最低输出电压央求。这下降了 SoC 的静态功耗,并愿意为最大愿意电压留出更大的余量。 |